Let’s discuss the question: how to debug makefile error. We summarize all relevant answers in section Q&A of website Achievetampabay.org in category: Blog Finance. See more related questions in the comments below.

What is := in makefile?

= defines a recursively-expanded variable. := defines a simply-expanded variable.

What is $@ makefile?

The $@ and $< are called automatic variables. The variable $@ represents the name of the target and $< represents the first prerequisite required to create the output file. For example: hello.o: hello.c hello.h gcc -c $< -o $@

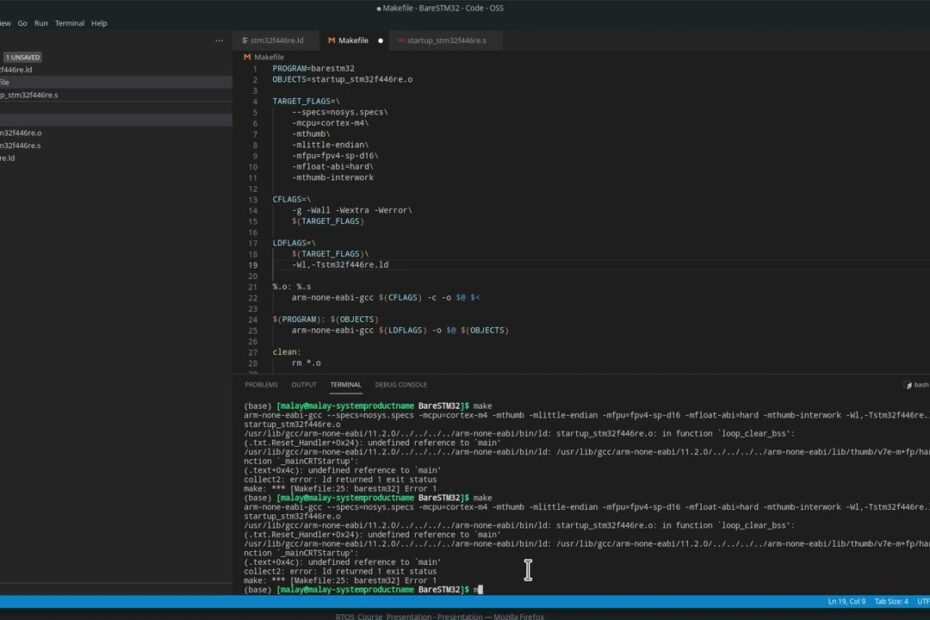

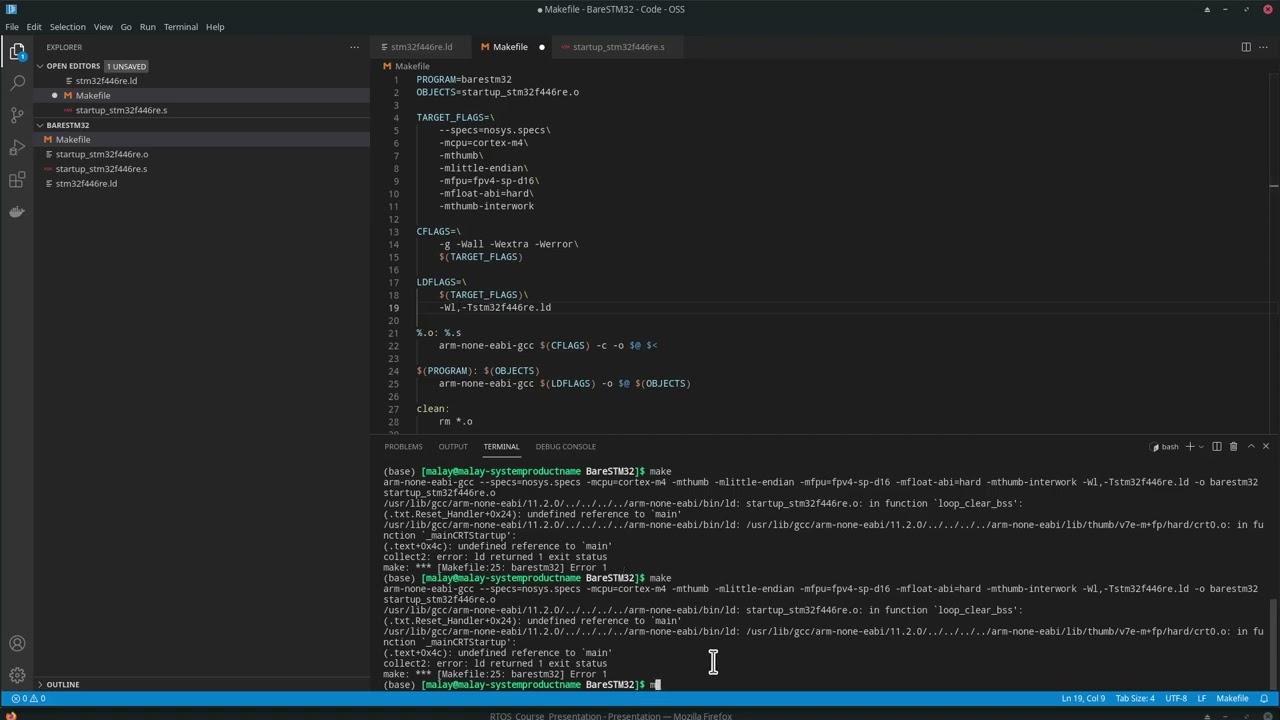

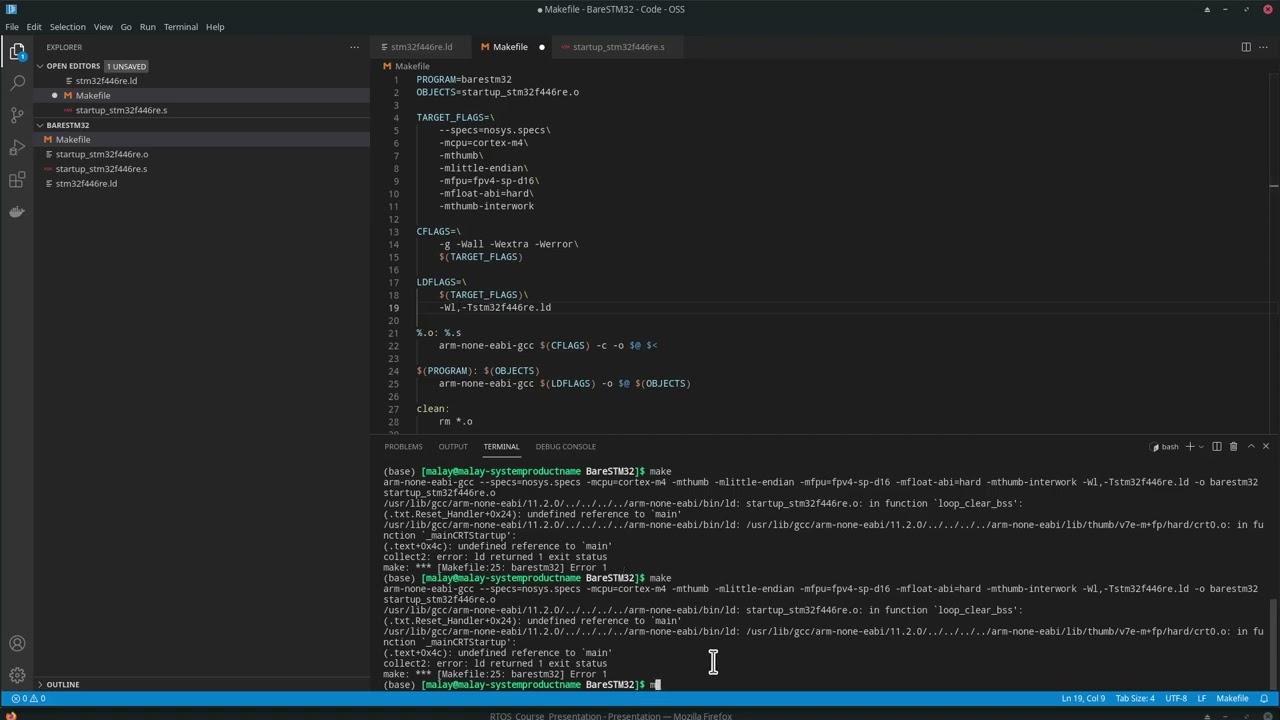

15. Debugging an error in Makefile

Images related to the topic15. Debugging an error in Makefile

What is @echo in makefile?

The ‘ @ ‘ is discarded before the line is passed to the shell. Typically you would use this for a command whose only effect is to print something, such as an echo command to indicate progress through the makefile: @echo About to make distribution files.

How do I run a makefile in Linux?

Also you can just type make if your file name is makefile/Makefile . Suppose you have two files named makefile and Makefile in the same directory then makefile is executed if make alone is given. You can even pass arguments to makefile.

How do I clean my makefile?

The Cleanup Rule clean: rm *.o prog3 This is an optional rule. It allows you to type ‘make clean’ at the command line to get rid of your object and executable files. Sometimes the compiler will link or compile files incorrectly and the only way to get a fresh start is to remove all the object and executable files.

What is .O file C++?

A .o object file file (also . obj on Windows) contains compiled object code (that is, machine code produced by your C or C++ compiler), together with the names of the functions and other objects the file contains. Object files are processed by the linker to produce the final executable.

What are the three essential elements of a Makefile?

Makefile contains: dependency rules, macros and suffix(or implicit) rules.

What is make command?

The make command invokes the execution of the makefile. It is a special file that contains the shell commands that we create to maintain the project. The makefile contains targets and commands for execution. It is not allowed to create more than one makefile. It is recommended to create a separate directory for it.

What type of file is Makefile?

Script written as a Makefile, a developer file type that is used for compiling and linking programs from source code files; stores instructions using the GNU make standard. NOTE: Makefiles more commonly are created with the filename Makefile, which does not have a file extension.

How do you debug a makefile variable?

To use it, just set the list of variables to print on the command line, and include the debug target: $ make V=”USERNAME SHELL” debug makefile:2: USERNAME = Owner makefile:2: SHELL = /bin/sh.exe make: debug is up to date. Now you can print variables by simply listing them on the command line.

What is makefile in C?

Makefile is a set of commands (similar to terminal commands) with variable names and targets to create object file and to remove them. In a single make file we can create multiple targets to compile and to remove object, binary files. You can compile your project (program) any number of times by using Makefile.

How do you make a wildcard in makefile?

If you want to do wildcard expansion in such places, you need to use the wildcard function, like this: $(wildcard pattern …) This string, used anywhere in a makefile, is replaced by a space-separated list of names of existing files that match one of the given file name patterns.

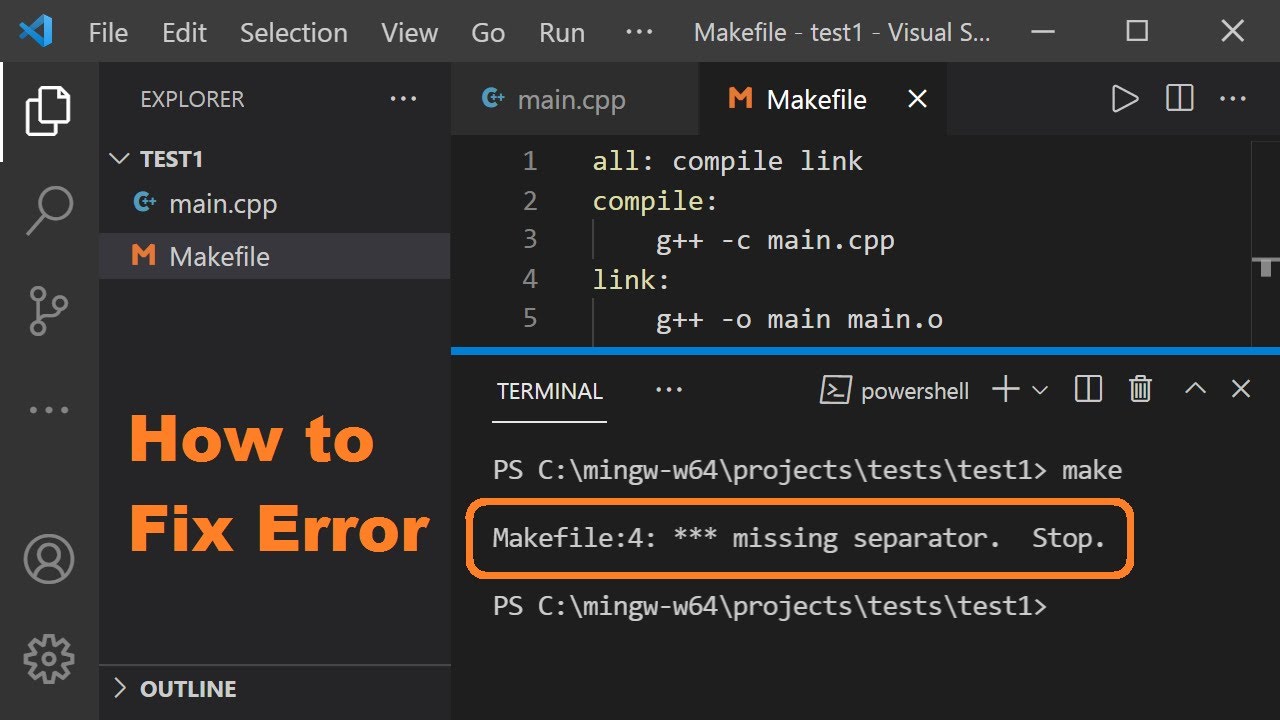

How to Fix Error Makefile: *** missing separator. Stop

Images related to the topicHow to Fix Error Makefile: *** missing separator. Stop

How do I run a makefile in Linux terminal?

…

Beta Program.

| Option | Meaning |

|---|---|

| -f FILE | Reads FILE as the makefile. |

| -h | Displays the list of make options. |

| -i | Ignores all errors in commands executed when building a target. |

How do you set a variable in makefile?

- A variable is a name defined in a makefile to represent a string of text, called the variable’s value. …

- To substitute a variable’s value, write a dollar sign followed by the name of the variable in parentheses or braces: either `$(foo)’ or `${foo}’ is a valid reference to the variable foo .

How do I run AC script in terminal?

- Open up a terminal. Search for the terminal application in the Dash tool (located as the topmost item in the Launcher). …

- Use a text editor to create the C source code. Type the command. …

- Compile the program. …

- Execute the program.

How do I edit a Makefile?

- Log in as a superuser.

- Modify the line that starts with the word all by adding the name(s) of the database you want to add: …

- Add the following lines at the end of the Makefile : …

- Add an entry for auto_direct. …

- Run make .

What does rm command do?

The rm command is used to delete files. rm -i will ask before deleting each file. Some people will have rm aliased to do this automatically (type “alias” to check).

What is Flag in rm command?

As rm is a very destructive command, you may accidentally remove important files. The good news is that, rm has an -i flag which prompts (to confirm) you before removing every file. For example, let’s say, you want to remove the file hello.txt but you want rm to prompt you to confirm the file removal operation.

How a C++ program is executed?

There are three steps in executing a c++ program: Compiling, Linking and Running the program. The c++ programs have to be typed in a compiler. All the programs discussed in the book will be compiled on turbo c++ compiler. The turbo c++ compiler comes with an editor to type and edit c++ program.

Can C++ compile atom?

This Atom package allows you to compile and run C++ and C within the editor. To compile C or C++, press F5 or right click the file in tree view and click Compile and Run .

How C++ is compiled?

The compiler parses the pure C++ source code (now without any preprocessor directives) and converts it into assembly code. Then invokes underlying back-end(assembler in toolchain) that assembles that code into machine code producing actual binary file in some format(ELF, COFF, a.

What is the flag in GCC?

| Flag | Purpose | Applicable Fedora versions |

|---|---|---|

| -fstack-protector-strong | Likewise | All |

| -g | Generate debugging information | All |

| -grecord-gcc-switches | Store compiler flags in debugging information | All |

| -mcet -fcf-protection | Control flow integrity protection | 28 and later (x86 only) |

C++ Tutorial for Beginners #10: Debugging Makefile Project with Visual Studio Code IDE | (Linux GDB)

Images related to the topicC++ Tutorial for Beginners #10: Debugging Makefile Project with Visual Studio Code IDE | (Linux GDB)

What is in GNU make?

GNU Make is a tool which controls the generation of executables and other non-source files of a program from the program’s source files. Make gets its knowledge of how to build your program from a file called the makefile, which lists each of the non-source files and how to compute it from other files.

What is Patsubst in makefile?

$(patsubst PATTERN,REPLACEMENT,TEXT) Finds whitespace-separated words in TEXT that match PATTERN and replaces them with REPLACEMENT. Here PATTERN may contain a % which acts as a wildcard, matching any number of any characters within a word.

Related searches

- make options

- Vscode debug c++ makefile

- Make debug mode

- Variable makefile

- Print in makefile

- how to debug makefile

- Debug makefile

- how to debug an error in visual studio

- how to run makefile

- Warning makefile

- variable makefile

- warning makefile

- debug makefile

- how to exit makefile when error

- vscode debug c makefile

- print in makefile

- make debug mode

Information related to the topic how to debug makefile error

Here are the search results of the thread how to debug makefile error from Bing. You can read more if you want.

You have just come across an article on the topic how to debug makefile error. If you found this article useful, please share it. Thank you very much.