Let’s discuss the question: how to install icarus verilog. We summarize all relevant answers in section Q&A of website Achievetampabay.org in category: Blog Finance. See more related questions in the comments below.

How do I install Icarus?

Stable Version

Prepackaged versions of the Icarus Verilog stable releases are available via the openSUSE build service. Simply browse to software.opensuse.org, search for verilog, and click the install button for the version you wish to install.

Is Icarus Verilog good?

I wouldn’t recommend Icarus Verilog, it’s not a very good simulator. You’re much… | Hacker News. I wouldn’t recommend Icarus Verilog, it’s not a very good simulator. You’re much better off downloading either the free Altera/IntelFPGA copy of Modelsim or using the free version of Xilinx’s Vivado.

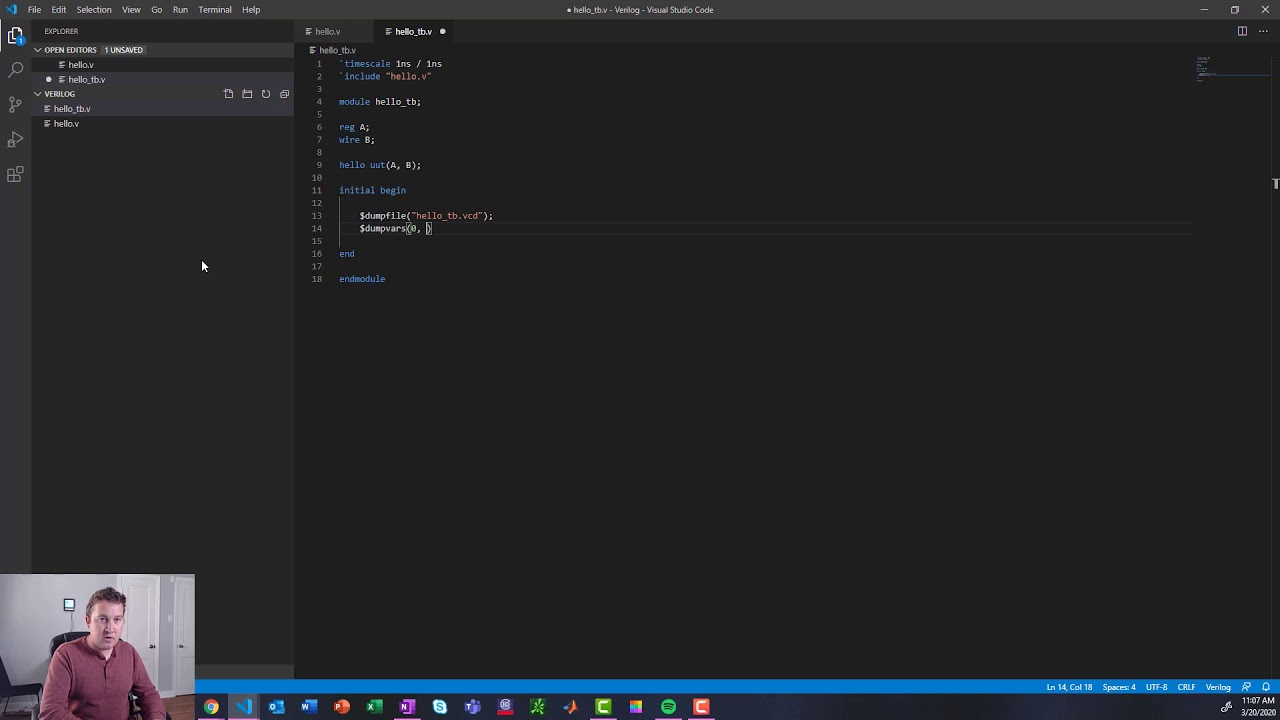

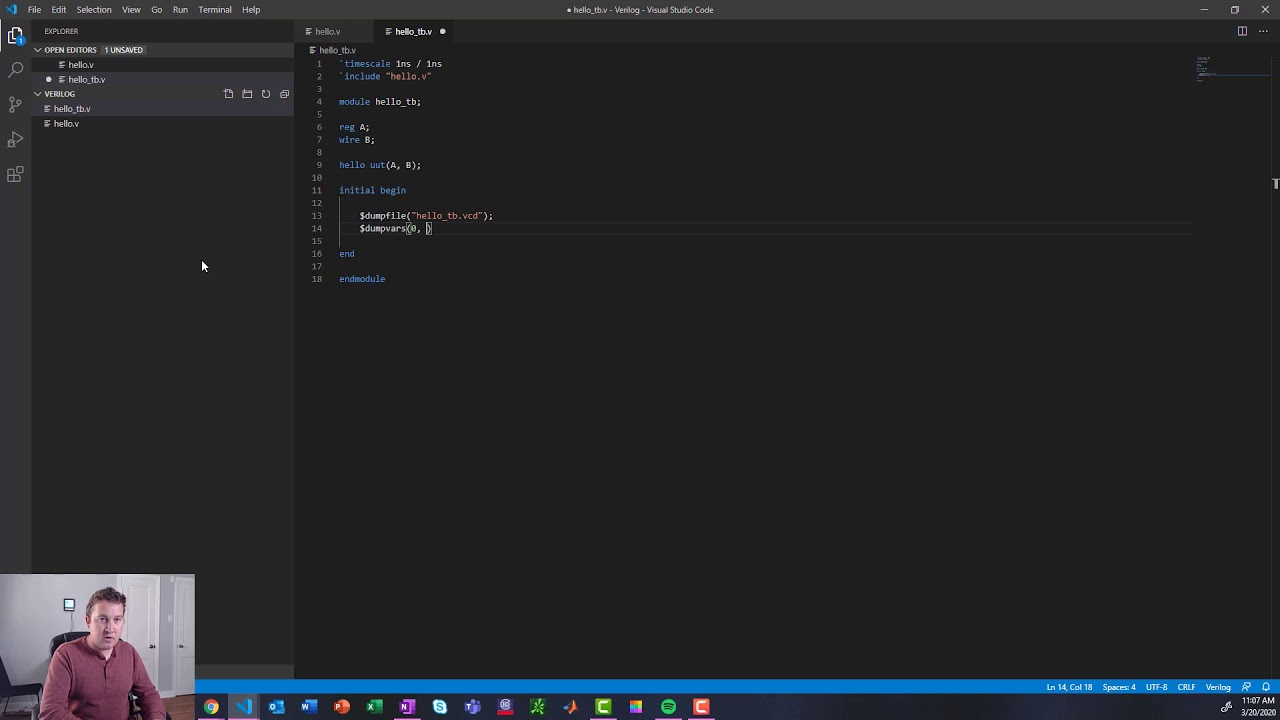

Verilog HDL – Installing and Testing Icarus Verilog + GTKWave

Images related to the topicVerilog HDL – Installing and Testing Icarus Verilog + GTKWave

How do I run a Verilog file?

- Compile from source on Linux/Mac or in Cygwin on Windows. You will need make, autoconf, gcc, g++, flex, bison to compile (and maybe more depending on your system).

- Install on MacOS using Homebrew.

- Install on Ubuntu using aptitude.

- Example 1. Save this verilog code as hello.v.

- Example 2. Save the code below as alu.v.

How do I open a GTKWave file?

To open a waveform with GTKWave on Linux, run gtkwave /path/to/wave. vcd. On Mac, if you’re using GTKWave, you can open the GTKWave application, and then use file → open new window to access the file.

How do I run GTKWave on Windows?

Download GTKWave and all_libs from dspia.com/gtkwave.html as Martin Thompson suggested. Then unzip everything into the same folder. The important thing to make it run under Windows is to put the executable gtkwave.exe into the subfolder all_libs/bin (this is were all the . dlls are located) or to add it to your path.

How do you compile in Verilog?

2.3 Compile the Verilog file

After writing the code, go to the Project tab and right-click on the file in use. From the menu select <Compile à Compile Selected>, and note the Transcript window and the file status.

What is iverilog command?

The iverilog command is the compiler/driver that takes the Verilog input and generates the output format, whether the simulation file or synthesis results. This information is at least summarized in the iverilog man page distributed in typical installations, but here we try to include more detail.

How do I get Visual Studio code for Verilog?

Make sure svls is in your $PATH environmental variable. Experimental support. Enable logging for this extension. Open the Output pane in VS Code and choose Verilog in the drop-down menu to view the log.

What is SystemVerilog used for?

SystemVerilog, standardized as IEEE 1800, is a hardware description and hardware verification language used to model, design, simulate, test and implement electronic systems.

Does Verilator support SystemVerilog?

Verilator converts synthesizable Verilog to C++ or SystemC. It can handle all versions of Verilog and also some SystemVerilog and Sugar/PSL assertions.

What is the use of Verilog HDL?

You can use Verilog HDL for designing hardware and for creating test entities to verify the behavior of a piece of hardware. Verilog HDL is used as an entry format by a variety of EDA tools, including synthesis tools such as Quartus® Prime Integrated Synthesis, simulation tools, and formal verification tools.

Icarus verilog + GTKWave installing and running | Free software for verilog HDL

Images related to the topicIcarus verilog + GTKWave installing and running | Free software for verilog HDL

How do I run Icarus Verilog on Windows?

The Windows program can be downloaded from http://bleyer.org/icarus/ ( Opens in a new tab) – . This site results in the google when you search for “Icarus Verilog download”. Double click the downloaded setup file and fillow the instructions to install the verilog on your windows.

Where do Verilog codes run?

- Crimson.

- Eclipse.

- Github.

- Solarized.

- Cobalt.

- krTheme.

- Monokai.

- Terminal.

Which software is used for Verilog?

| Simulator name | License | Author/company |

|---|---|---|

| Cascade | BSD | VMware Research |

| GPL Cver | GPL | Pragmatic C Software |

| Icarus Verilog | GPL2+ | Stephen Williams |

| Isotel Mixed Signal & Domain Simulation | GPL | ngspice and Yosys communities, and Isotel |

How do I run GTKWave on Mac?

- To install gtkwave, run the following command in macOS terminal (Applications->Utilities->Terminal) sudo port install gtkwave Copy.

- To see what files were installed by gtkwave, run: port contents gtkwave Copy.

- To later upgrade gtkwave, run: sudo port selfupdate && sudo port upgrade gtkwave Copy.

How do I play a VCD file?

- Launch Windows Media Player.

- Insert the VCD in to the CD Drive.

- From the menu bar, select the VCD you want to play.

- If it doesn’t begin playing automatically, press the Play (>) button.

- Adjust the screen size.

How do you show a waveform in Verilog?

Go to Start -> Computer ->Properties -> Advanced System Settings -> Environment Variable -> System Variable and click on the variable named path and then click edit. Now add C:\iverilog\gtkwave\bin; We will now extend our comparator example to see how we can use the gtkwave to view waveform.

How do I run a Verilog code on EDA playground?

- Go to your code on EDA Playground. For example: RAM Design and Test.

- Make sure your code contains appropriate function calls to create a *.vcd file. For example: …

- Select a simulator and check the Open EPWave after run checkbox. …

- Click Run.

How do I create a VCD file in Verilog?

- $dumpfile(“file_name. vcd”) => To generate vcd file with specified name. …

- $dumpvars(0, top) => To specify which variables to be dumped into vcd file.

How do you make a testbench in Verilog?

- Create a Testbench Module. The first thing we do in the testbench is declare an empty module to write our testbench code in. …

- Instantiate the DUT. …

- Generate the Clock and Reset. …

- Write the Stimulus.

What is compilation Verilog?

The compile step is part of a tool’s process of reading that source HDL into a form that the tool can act upon. Both simulation and synthesis tool go through the compilation process which create an internal data structure most suitable to the task.

iCARUS Verilog – Installation – Getting Started – Beginner – Hello World

Images related to the topiciCARUS Verilog – Installation – Getting Started – Beginner – Hello World

What is VVP Verilog?

vvp is the run time engine that executes the default compiled form generated by Icarus Verilog. The output from the iverilog command is not by itself executable on any platform. Instead, the vvp program is invoked to execute the generated output file.

How do you input a clock in Verilog?

- convert first assign into initial begin clk = 0; end.

- second assign to always.

- make clk reg type.

Related searches

- iverilog

- icarus verilog

- icarus verilog download

- verilog tutorial pdf

- Icarus Verilog download

- Install iverilog

- how to run icarus verilog

- Icarus Verilog

- install iverilog

- how to install icarus verilog on windows

- verilog visual studio code

- how to install icarus verilog on windows 10

- Verilog compiler

- Verilog visual studio code

- verilog for mac

- verilog compiler

- Verilog for Mac

Information related to the topic how to install icarus verilog

Here are the search results of the thread how to install icarus verilog from Bing. You can read more if you want.

You have just come across an article on the topic how to install icarus verilog. If you found this article useful, please share it. Thank you very much.